LC2K Cache Simulator

Computer Architecture

Project details

Description

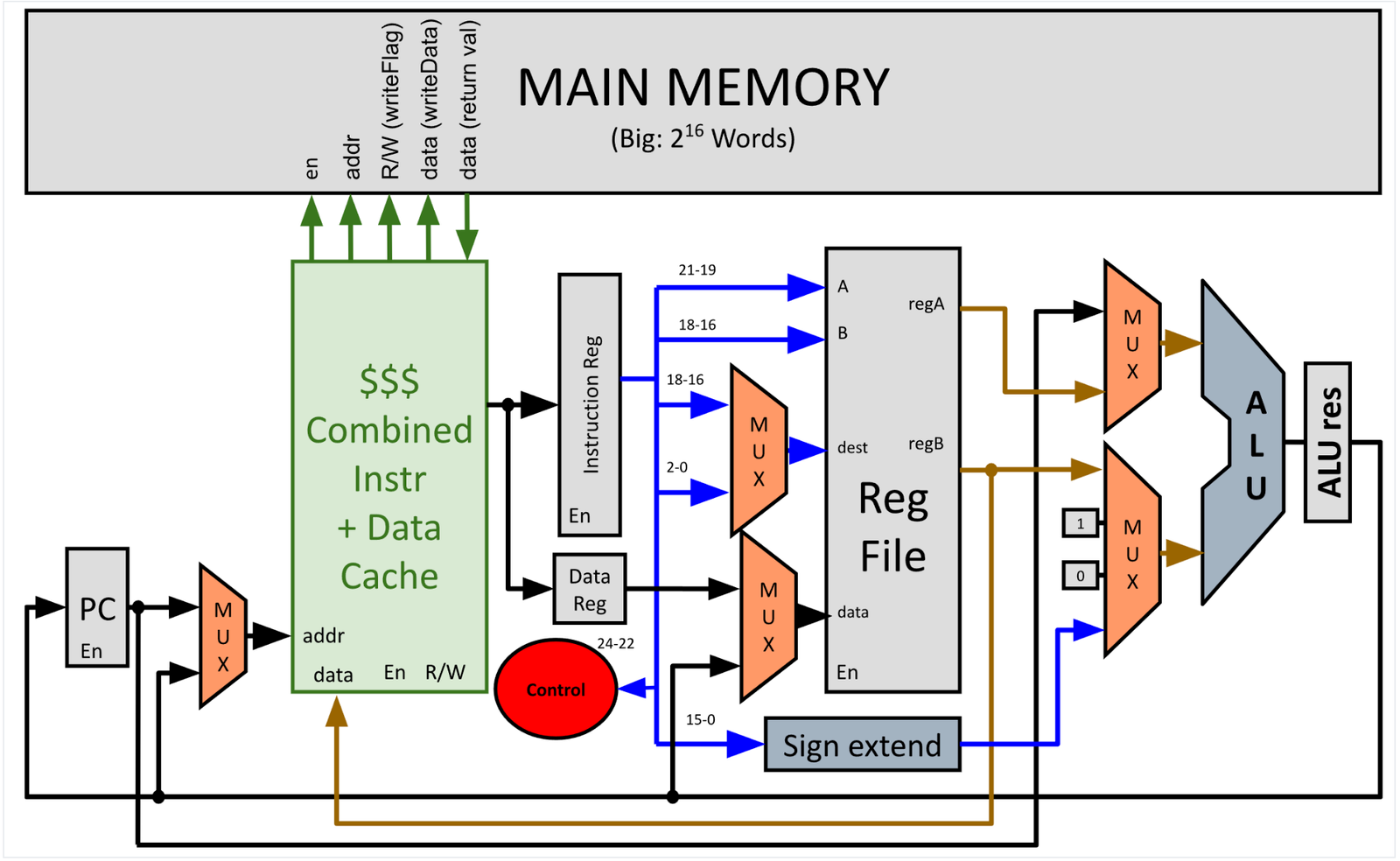

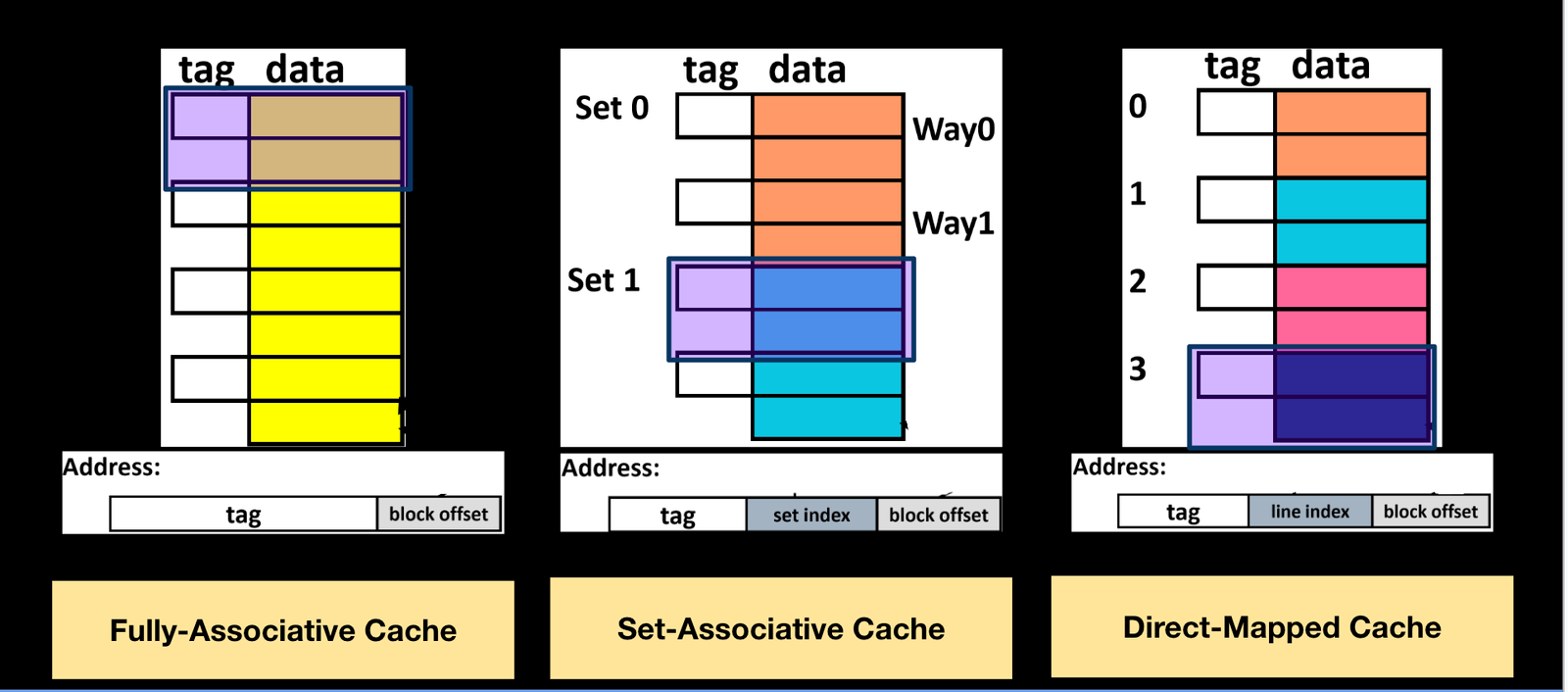

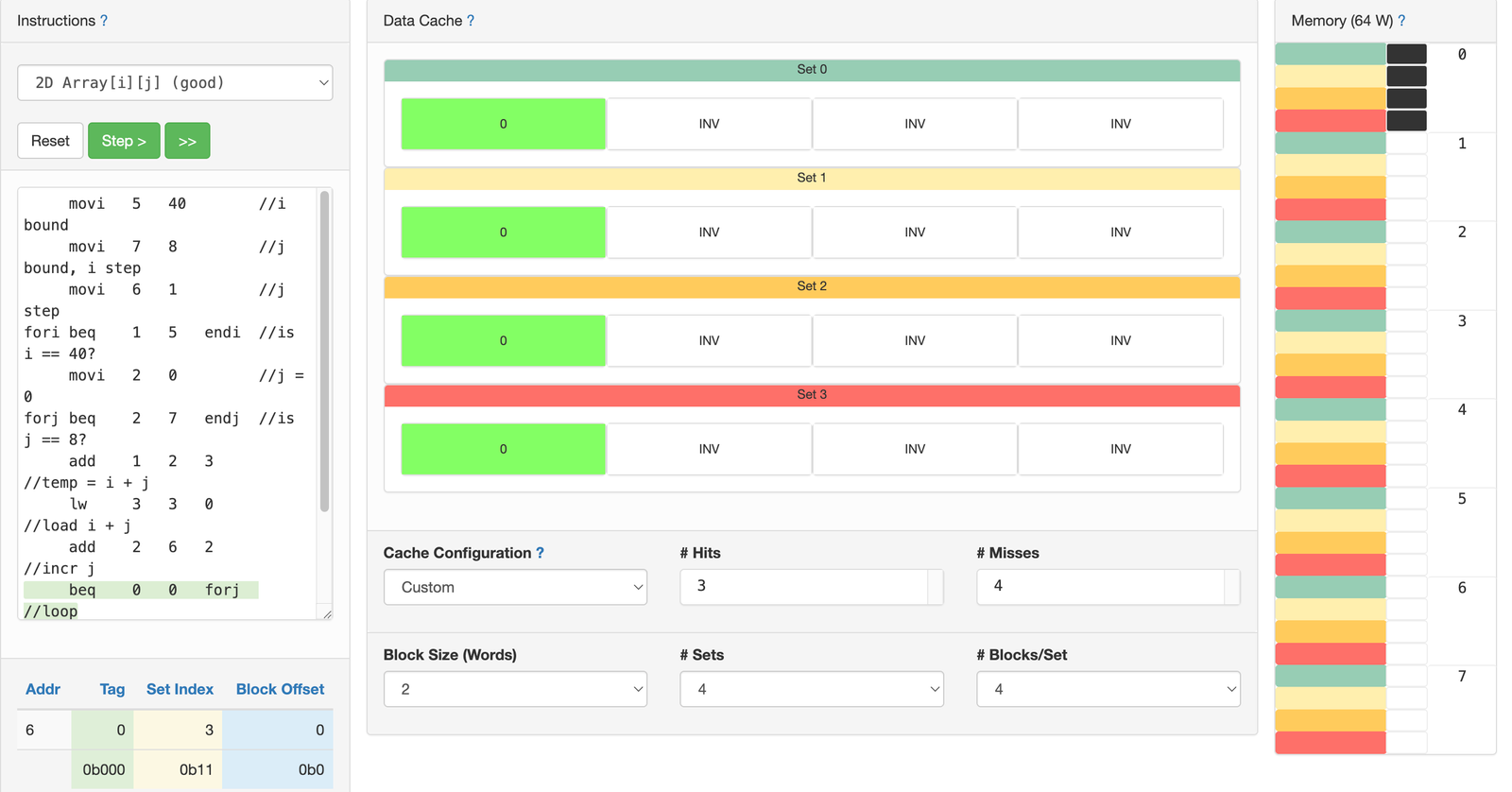

Extended my pipelined LC‑2K simulator in C to model a unified instruction/data cache accurately:

- Implemented configurable block size, associativity, write‑back policy, and LRU replacement

- Logged cache hits, misses, write‑backs, and memory transfers via printAction() for full visibility

- Integrated the cache into the pipeline, handling stalls on misses and write‑back delays

- Validated correctness with a robust test suite covering mapping conflicts, eviction behavior, and data write policies

📸 Photos sourced from official EECS370 lecture/lab slides.

-

Start Date:

Apr 4th, 2025 -

End Date:

Apr 18th, 2025 -

Github:

Private -

Course:

EECS370 -

Course Topic:

Computer Architecture

7+

Years of Coding Experience

25

Completed CS Projects

3+